Project 3

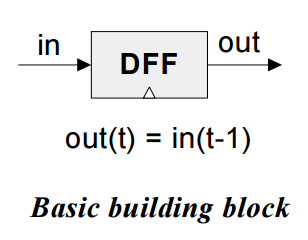

DFF

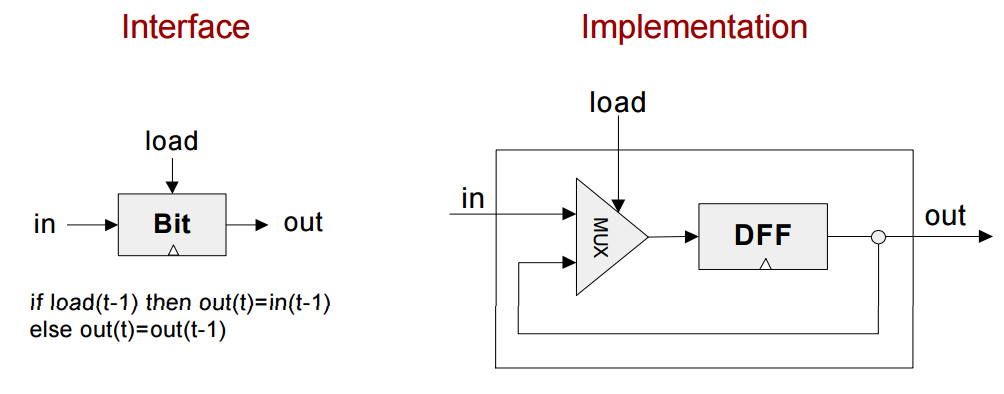

Bit

CHIP Bit {

IN in, load;

OUT out;

PARTS:

Mux(a=D,b=in,sel=load,out=F);

DFF(in=F,out=D,out=out);

}

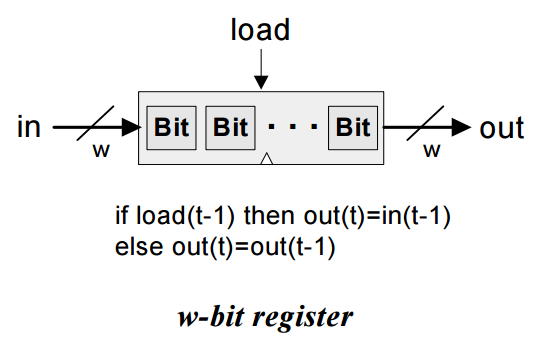

Register

CHIP Register {

IN in[16], load;

OUT out[16];

PARTS:

Bit(in=in[00],load=load,out=out[00]);

Bit(in=in[01],load=load,out=out[01]);

Bit(in=in[02],load=load,out=out[02]);

Bit(in=in[03],load=load,out=out[03]);

Bit(in=in[04],load=load,out=out[04]);

Bit(in=in[05],load=load,out=out[05]);

Bit(in=in[06],load=load,out=out[06]);

Bit(in=in[07],load=load,out=out[07]);

Bit(in=in[08],load=load,out=out[08]);

Bit(in=in[09],load=load,out=out[09]);

Bit(in=in[10],load=load,out=out[10]);

Bit(in=in[11],load=load,out=out[11]);

Bit(in=in[12],load=load,out=out[12]);

Bit(in=in[13],load=load,out=out[13]);

Bit(in=in[14],load=load,out=out[14]);

Bit(in=in[15],load=load,out=out[15]);

}

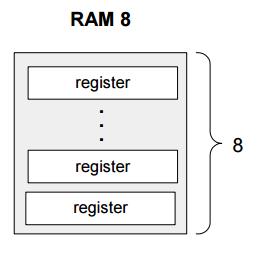

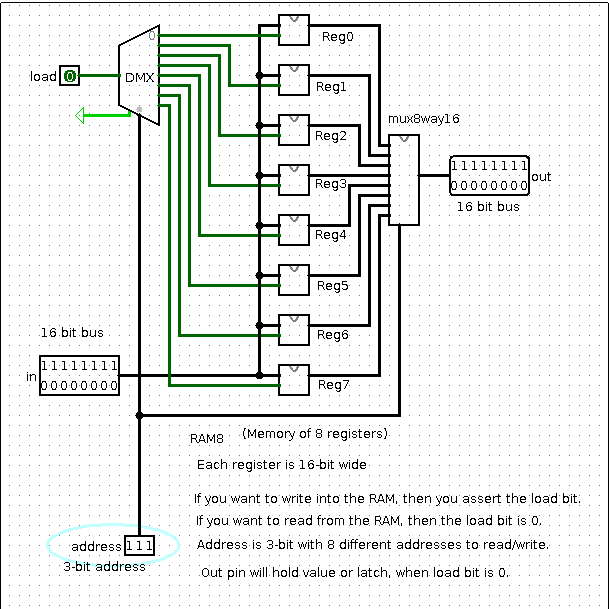

RAM8

CHIP RAM8 {

IN in[16], load, address[3];

OUT out[16];

PARTS:

DMux8Way(in=load,sel=address,a=loada,b=loadb,c=loadc,d=loadd,e=loade,f=loadf,g=loadg,h=loadh);

Register(in=in,load=loada,out=outa);

Register(in=in,load=loadb,out=outb);

Register(in=in,load=loadc,out=outc);

Register(in=in,load=loadd,out=outd);

Register(in=in,load=loade,out=oute);

Register(in=in,load=loadf,out=outf);

Register(in=in,load=loadg,out=outg);

Register(in=in,load=loadh,out=outh);

Mux8Way16(a=outa,b=outb,c=outc,d=outd,e=oute,f=outf,g=outg,h=outh,sel=address,out=out);

}

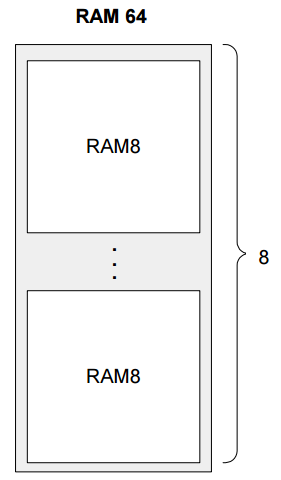

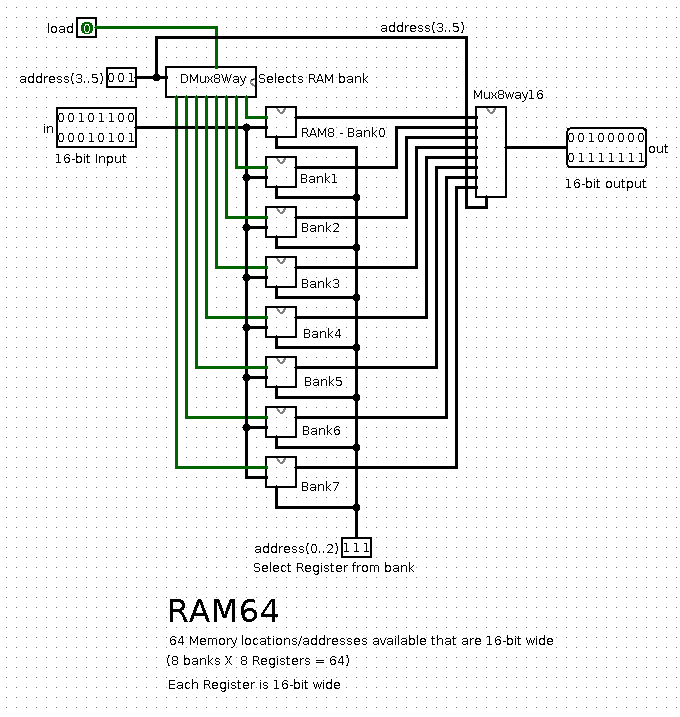

RAM64

CHIP RAM64 {

IN in[16], load, address[6];

OUT out[16];

PARTS:

DMux8Way(in=load,sel=address[3..5],a=loada,b=loadb,c=loadc,d=loadd,e=loade,f=loadf,g=loadg,h=loadh);

RAM8(in=in,load=loada,address=address[0..2],out=outa);

RAM8(in=in,load=loadb,address=address[0..2],out=outb);

RAM8(in=in,load=loadc,address=address[0..2],out=outc);

RAM8(in=in,load=loadd,address=address[0..2],out=outd);

RAM8(in=in,load=loade,address=address[0..2],out=oute);

RAM8(in=in,load=loadf,address=address[0..2],out=outf);

RAM8(in=in,load=loadg,address=address[0..2],out=outg);

RAM8(in=in,load=loadh,address=address[0..2],out=outh);

Mux8Way16(a=outa,b=outb,c=outc,d=outd,e=oute,f=outf,g=outg,h=outh,sel=address[3..5],out=out);

}

RAM512

CHIP RAM512 {

IN in[16], load, address[9];

OUT out[16];

PARTS:

DMux8Way(in=load,sel=address[6..8],a=loada,b=loadb,c=loadc,d=loadd,e=loade,f=loadf,g=loadg,h=loadh);

RAM64(in=in,load=loada,address=address[0..5],out=outa);

RAM64(in=in,load=loadb,address=address[0..5],out=outb);

RAM64(in=in,load=loadc,address=address[0..5],out=outc);

RAM64(in=in,load=loadd,address=address[0..5],out=outd);

RAM64(in=in,load=loade,address=address[0..5],out=oute);

RAM64(in=in,load=loadf,address=address[0..5],out=outf);

RAM64(in=in,load=loadg,address=address[0..5],out=outg);

RAM64(in=in,load=loadh,address=address[0..5],out=outh);

Mux8Way16(a=outa,b=outb,c=outc,d=outd,e=oute,f=outf,g=outg,h=outh,sel=address[6..8],out=out);

}

RAM4K

CHIP RAM4K {

IN in[16], load, address[12];

OUT out[16];

PARTS:

DMux8Way(in=load,sel=address[9..11],a=loada,b=loadb,c=loadc,d=loadd,e=loade,f=loadf,g=loadg,h=loadh);

RAM512(in=in,load=loada,address=address[0..8],out=outa);

RAM512(in=in,load=loadb,address=address[0..8],out=outb);

RAM512(in=in,load=loadc,address=address[0..8],out=outc);

RAM512(in=in,load=loadd,address=address[0..8],out=outd);

RAM512(in=in,load=loade,address=address[0..8],out=oute);

RAM512(in=in,load=loadf,address=address[0..8],out=outf);

RAM512(in=in,load=loadg,address=address[0..8],out=outg);

RAM512(in=in,load=loadh,address=address[0..8],out=outh);

Mux8Way16(a=outa,b=outb,c=outc,d=outd,e=oute,f=outf,g=outg,h=outh,sel=address[9..11],out=out);

}

RAM16K

CHIP RAM16K {

IN in[16], load, address[14];

OUT out[16];

PARTS:

DMux4Way(in=load,sel=address[12..13],a=loada,b=loadb,c=loadc,d=loadd);

RAM4K(in=in,load=loada,address=address[0..11],out=outa);

RAM4K(in=in,load=loadb,address=address[0..11],out=outb);

RAM4K(in=in,load=loadc,address=address[0..11],out=outc);

RAM4K(in=in,load=loadd,address=address[0..11],out=outd);

Mux4Way16(a=outa,b=outb,c=outc,d=outd,sel=address[12..13],out=out);

}

PC

CHIP PC {

IN in[16],load,inc,reset;

OUT out[16];

PARTS:

Inc16(in=m0,out=m1);

Mux16(a=m0,b=m1,sel=inc,out=m2);

Mux16(a=m2,b=in,sel=load,out=m3);

Mux16(a=m3,b=false,sel=reset,out=m4);

Register(in=m4,load=true,out=out,out=m0);

}